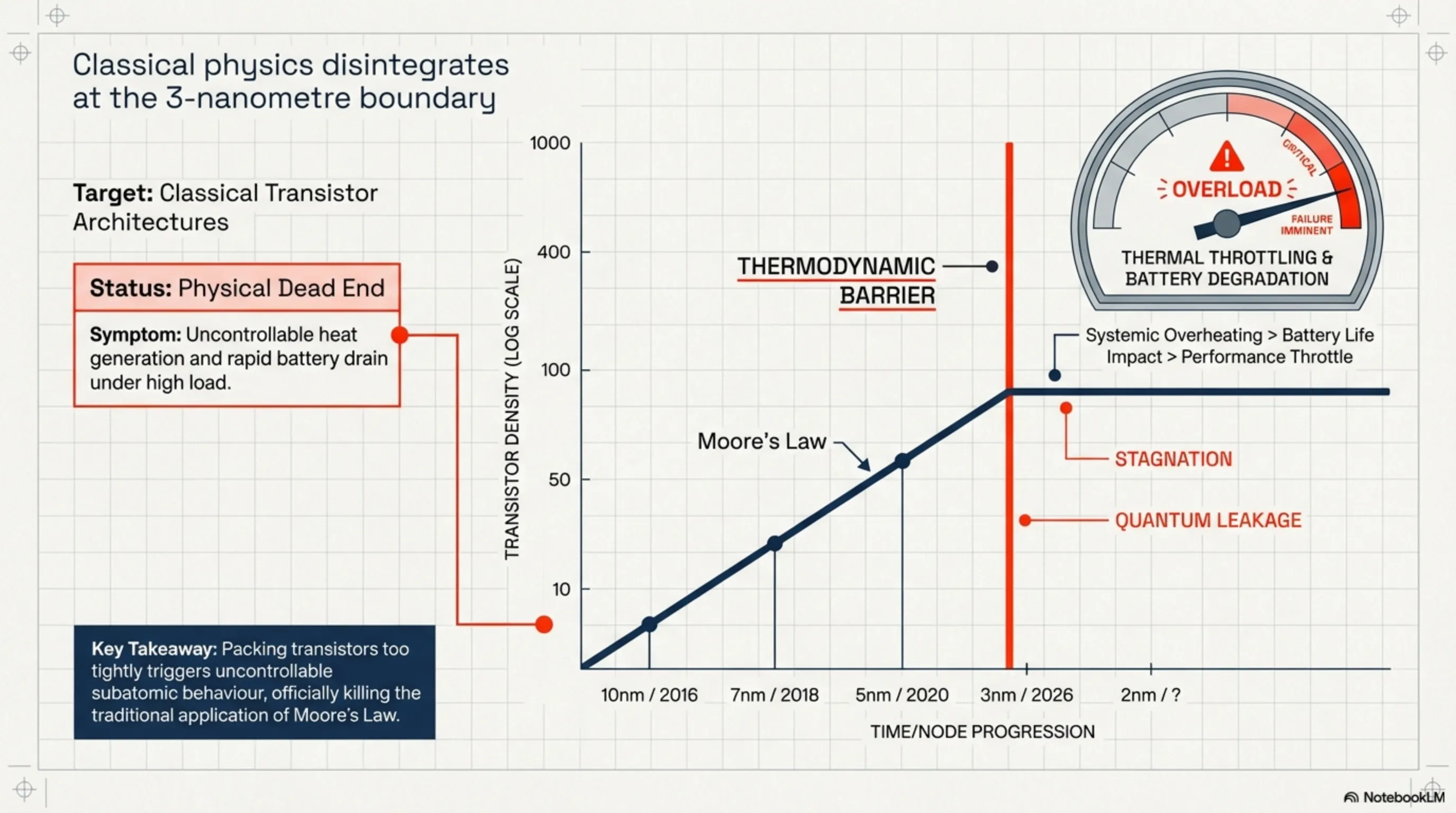

بیش از پنج دهه است که قانون مور (Moore's Law) به عنوان کتاب مقدسِ مهندسان سختافزار شناخته میشود؛ قانونی که پیشبینی میکرد تعداد ترانزیستورهای روی یک تراشه هر دو سال دو برابر خواهد شد. اما در سالهای اخیر، با رسیدنِ ابعاد ترانزیستورها به مرزهای فیزیک کوانتوم و ابعادِ اتمی، بسیاری از تحلیلگران پایانِ این قانون را اعلام کردند. اکنون در سال ۲۰۲۶، شرکت صنایع نیمههادی تایوان (TSMC) با راهاندازی خط تولید انبوه تراشههای ۲ نانومتری (گره N2)، نهتنها مرگِ قانون مور را به تعویق انداخته، بلکه قوانین فیزیک محاسباتی را در سیلیکونولی بازنویسی کرده است

درود بر ارتش تکین! بیش از نیم قرن است که صنعت تکنولوژی روی دوشِ قانونی به نام «مور» ایستاده است؛ قانونی که پیشبینی میکرد تعداد ترانزیستورها هر دو سال دو برابر میشود. اما امروز در سال ۲۰۲۶، ما در گاراژ تکین با حقیقتی خشن روبرو هستیم: فیزیک دیگر اجازه نمیدهد ترانزیستورها را به روش قدیمی کوچک کنیم. ما در حالِ عبور از مرزِ دنیای کلاسیک و ورود به قلمرویِ سیاه فیزیک کوانتوم هستیم. جایی که تراشههای ۲ نانومتری TSMC نه یک ارتقای ساده، بلکه یک معجزهی مهندسی برای بقا محسوب میشوند. آمادهی یک کالبدشکافی اتمی باشید؛ اینجا جایی است که سیلیکون، معنای جدیدی پیدا میکند!

[IMAGE_PLACEHOLDER_1]مقدمه: عبور از مرزهای فیزیک کوانتوم و بحرانِ ابعاد اتمی

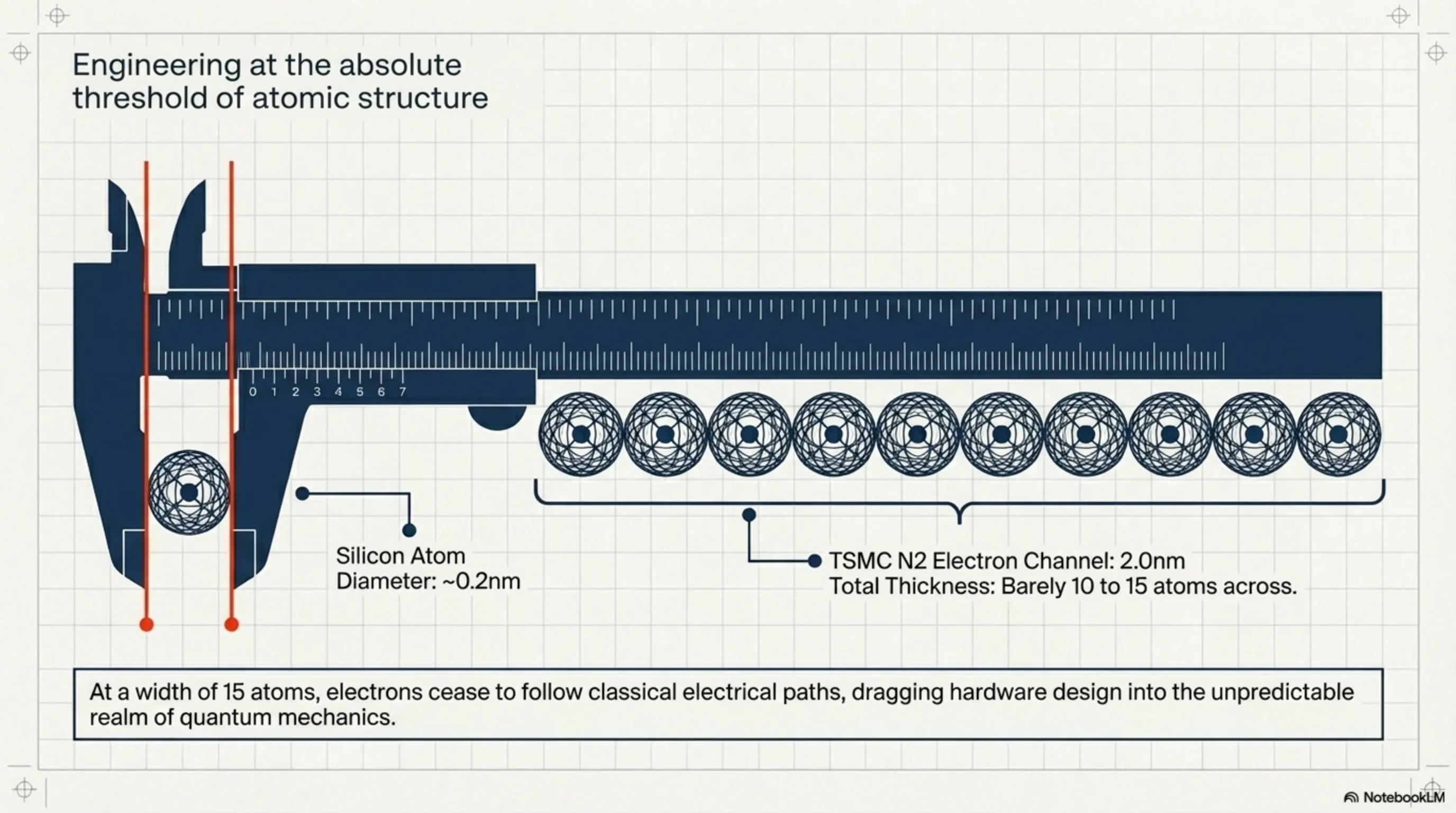

وقتی از عدد «۲ نانومتر» صحبت میکنیم، ذهنِ انسان به سختی میتواند عظمتِ این مقیاس را درک کند. برای اینکه تصوری داشته باشید، قطر یک رشتهی DNA انسانی حدود ۲.۵ نانومتر است. این یعنی مهندسان TSMC در حالِ ساختِ ساختارهایی هستند که از بلوکهای اصلیِ حیاتِ ما نیز کوچکترند! در این ابعاد، اتمهای سیلیکون به وضوح قابل شمارش هستند. ضخامتِ لایههایی که جریانِ الکتریسیته را در آیفون ۱۸ شما کنترل میکنند، تنها به اندازهی ۱۰ تا ۱۲ اتم سیلیکون است.

چرا این موضوع یک بحران است؟ زیرا در دنیایِ زیراتمی، الکترونها دیگر مثلِ آب درونِ لوله رفتار نمیکنند. همانطور که در تحلیلِ کنسولهای دستی ۲۰۲۶ اشاره کردیم، حتی تراشههای ۴ نانومتری مثل Z2 Extreme نیز با مشکلِ «نشت جریان» روبرو هستند. در مقیاس ۲ نانومتر، پدیدهای به نام «تونلزنی کوانتومی» (Quantum Tunneling) رخ میدهد. الکترونها به قدری به دیوارههای ترانزیستور نزدیک میشوند که طبقِ اصلِ عدمِ قطعیت، ناگهان از میانِ دیواره عبور کرده و در طرفِ دیگر ظاهر میشوند؛ بدونِ اینکه گیتِ کنترلی اجازه داده باشد! این فرارِ الکترونها یعنی نشتِ شدید برق، داغ شدنِ فاجعهبارِ تراشه و خالی شدنِ سریع باتری. گره پردازشی ۲ نانومتری TSMC عملاً تلاشی برای مهارِ این رفتارِ سرکشِ اتمهاست.

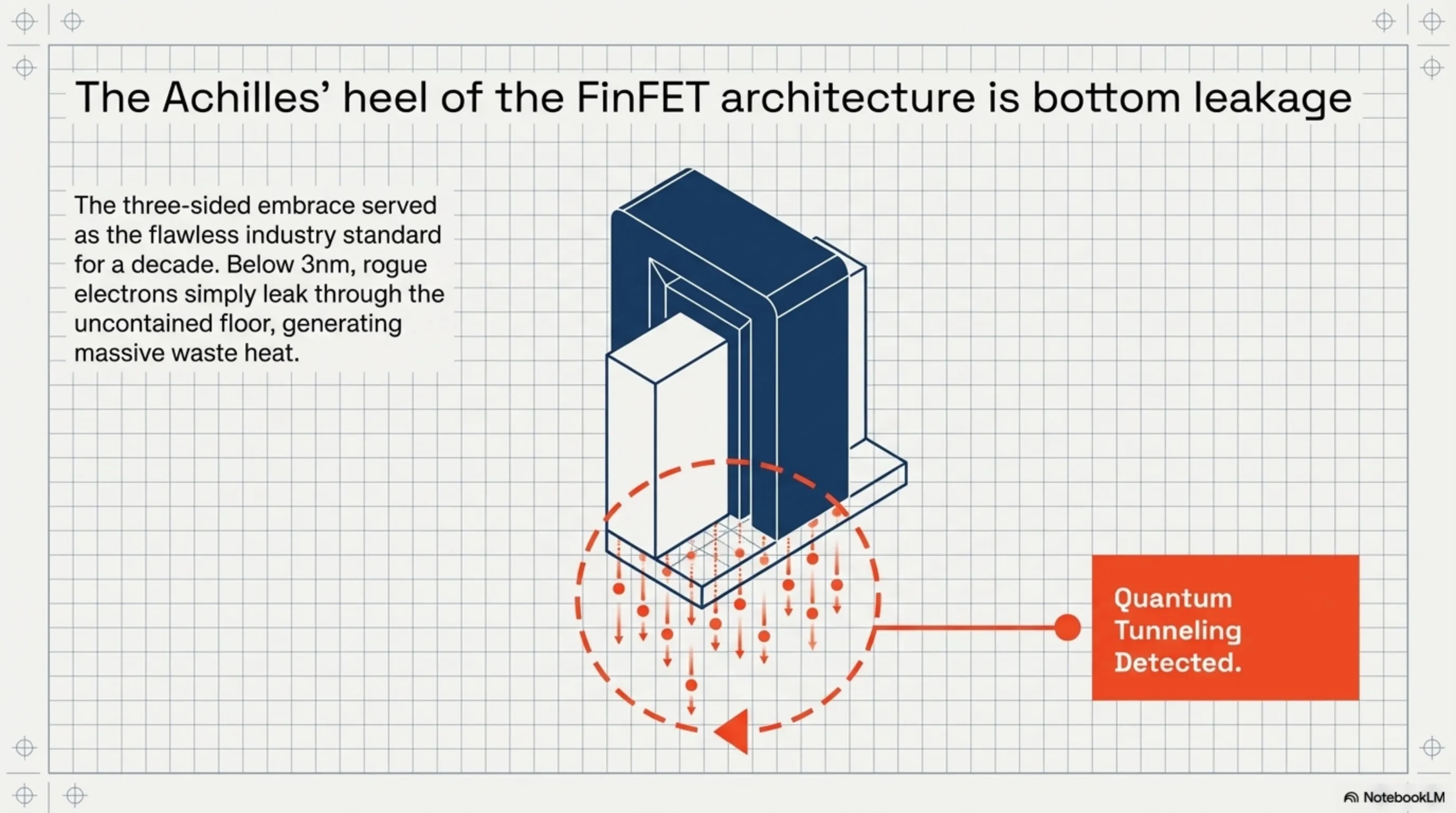

پایان امپراتوری FinFET؛ چرا بالههای سیلیکونی دیگر نمیتپند؟

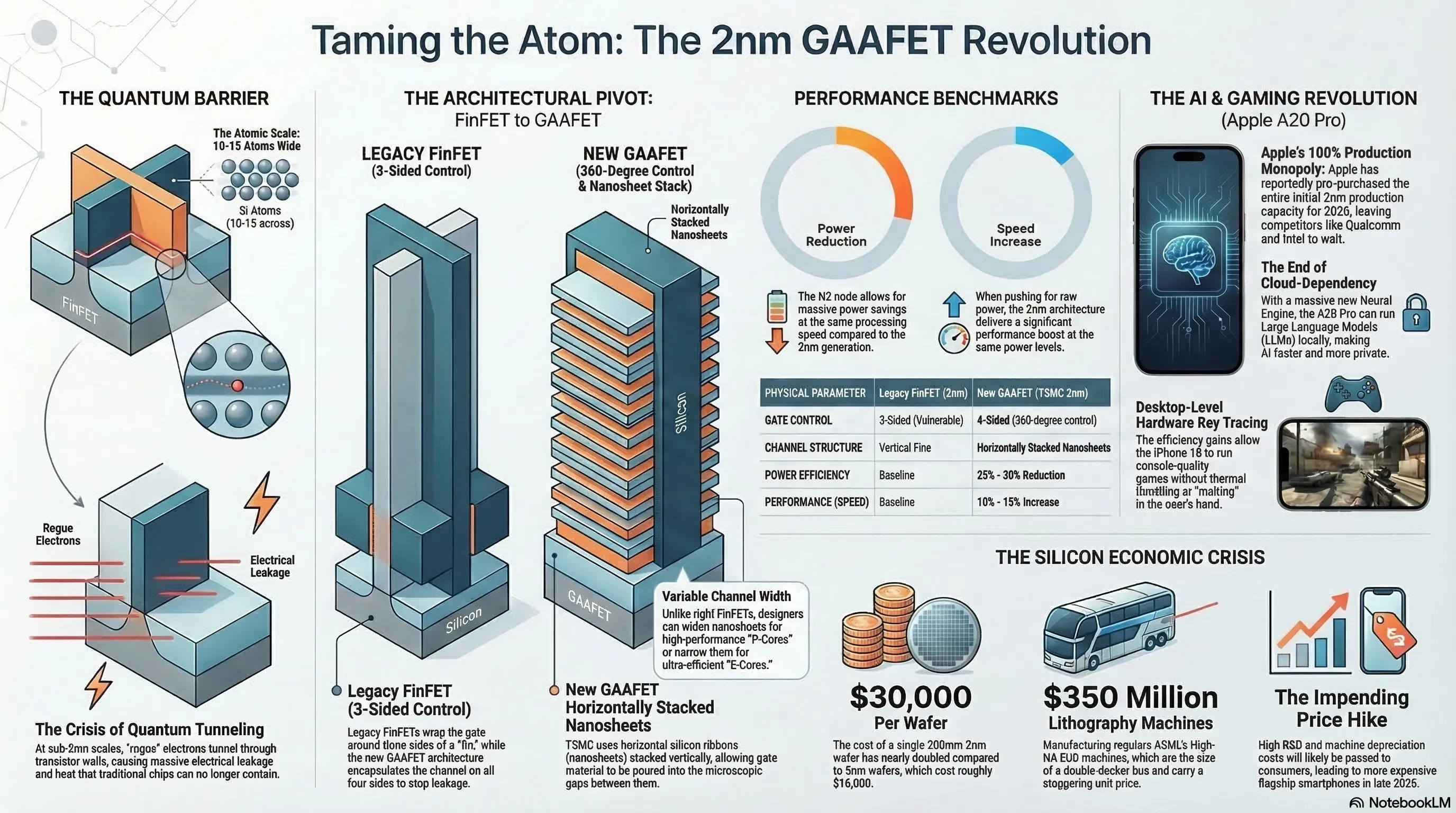

از سال ۲۰۱۲ تا به امروز، پادشاهِ بلامنازعِ دنیای تراشهها معماری FinFET (ترانزیستور بالهای) بود. در این طراحی، کانالِ عبور الکترون شبیه به بالهی کوسه از سطح سیلیکون بیرون زده بود و گیتِ کنترلی از سه طرف آن را احاطه میکرد. این معماری به ما اجازه داد از لیتوگرافیِ ۲۲ نانومتری تا ۳ نانومتری سفر کنیم. اما در مرزِ ۲ نانومتر، FinFET رسماً به پایانِ خط میرسد.

مشکلِ فنیِ FinFET در مقیاسهای کوچک، عدمِ کنترل روی «نشتِ جریان از کف» (Bottom Leakage) است. وقتی ترانزیستورها را بیش از حد فشرده میکنیم، آن یک وجهِ آزادِ باله که در تماس با بسترِ سیلیکونی است، به بزرگراهی برای فرار الکترونها تبدیل میشود. مهندسانِ TSMC در گاراژِ تحقیقاتیِ خود به این نتیجه رسیدند که برای مهارِ الکتریسیته در ابعادِ ۲ نانومتری، دیگر «سه طرف» کافی نیست؛ ما به یک محاصرهی کامل و ۳۶۰ درجهای نیاز داریم. اینجاست که معماریِ انقلابی GAAFET (Gate-All-Around) متولد میشود.

🔬 جدول مقایسه اتمی: FinFET در برابر GAAFET

| ویژگی فنی | FinFET (نسل قدیم) | GAAFET (نسل ۲ نانومتری) |

|---|---|---|

| کنترلِ گیت بر کانال | ۳ طرفه (U-Shape) | ۴ طرفه (۳۶۰ درجه کامل) |

| مهار نشت جریان | ضعیف در ابعاد زیر ۵ نانومتر | بسیار قدرتمند (حذف تونلزنی) |

| قابلیت تنظیم جریان | محدود (Discrete) | پیوسته (Variable Width) |

| ولتاژ کاری (Vdd) | بالا (تولید حرارت بیشتر) | بسیار پایین (بهینگی مصرف انرژی) |

مهندسی نانوصفحهها (Nanosheets)؛ جادوی ۳۶۰ درجه سیلیکون

در معماری GAAFET که TSMC برای گره ۲ نانومتری (N2) استفاده میکند، ما با مفهومی به نام «نانوصفحه» (Nanosheet) روبرو هستیم. تصور کنید به جای آن بالهی عمودیِ FinFET، حالا چندین لایهی افقی از سیلیکون (مثل ورقههای بسیار نازکِ کالباس!) روی هم قرار گرفتهاند. گیتِ کنترلی دقیقاً مانند مایعی که در درزها نفوذ میکند، دورِ تا دورِ این ورقهها را پر میکند. این یعنی الکترون برای عبور از کانال، توسطِ دیوارههای کنترلی کاملاً محاصره شده است.

برتریِ استراتژیکِ نانوصفحهها در این است که عرضِ این صفحهها قابل تنظیم است. در دنیای FinFET، اگر طراحِ تراشه (مثلاً تیمِ اپل) میخواست قدرتِ یک هسته را زیاد کند، مجبور بود تعدادِ بالهها را زیاد کند که فضایِ وحشتناکی اشغال میکرد. اما در معماریِ ۲ نانومتری، مهندسان میتوانند به سادگی عرضِ نانوصفحهها را کم یا زیاد کنند. برای هستههای فوقکممصرفِ آیفون ۱۸ از نانوصفحههای باریک استفاده میشود تا مصرف انرژی را به صفر نزدیک کنند، و برای هستههای گرافیکیِ سنگین از نانوصفحههای عریض استفاده میشود تا قدرتِ پردازشیِ بیرحمانهای را پمپاژ کنند. این سطح از شخصیسازی در سیلیکون، پیش از این هرگز ممکن نبود.

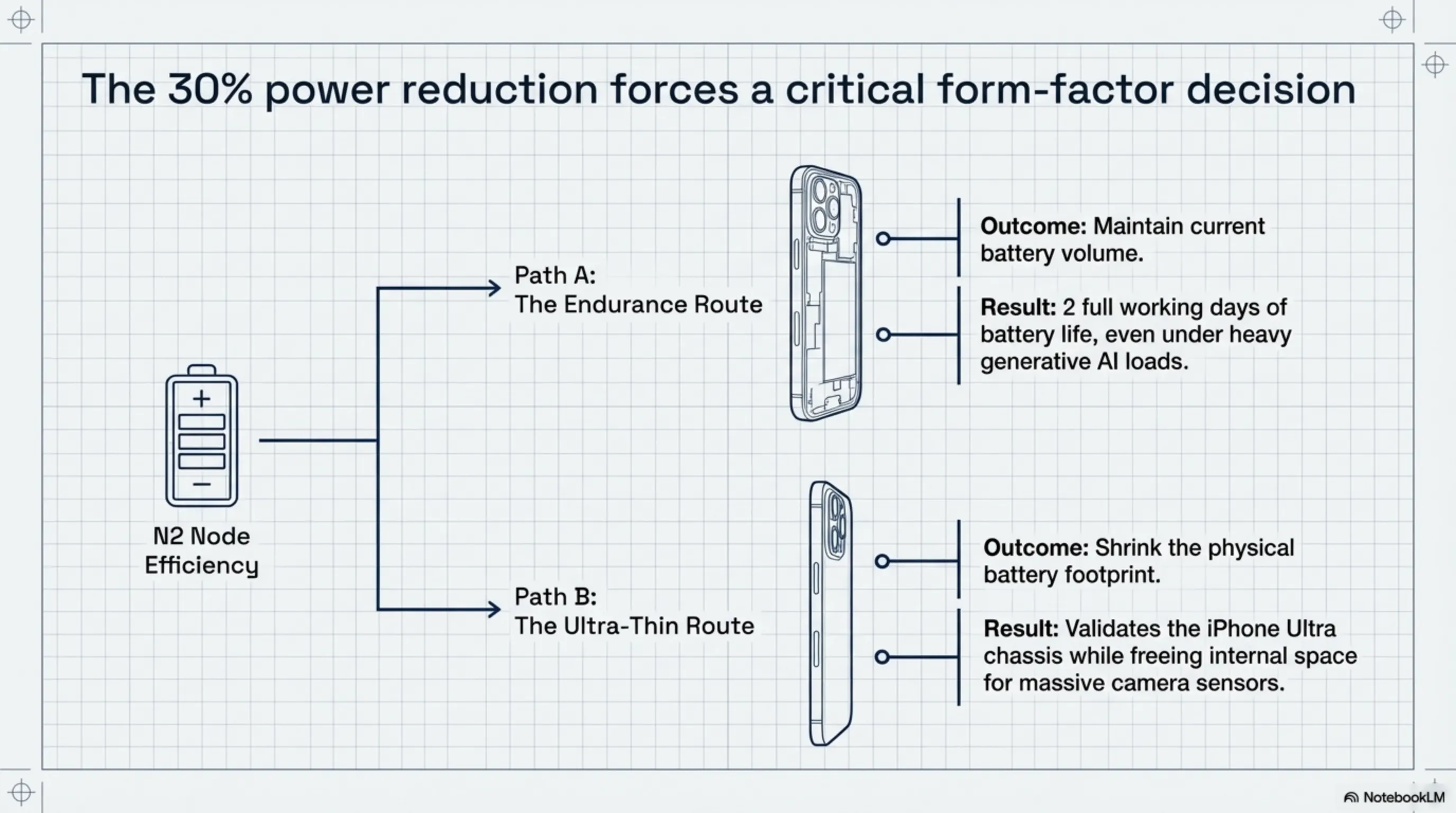

کالبدشکافیِ عمیقِ ما در گاراژ نشان میدهد که TSMC با گره N2، به افزایش ۱۰ تا ۱۵ درصدی عملکرد در توانِ یکسان، و یا کاهش ۲۵ تا ۳۰ درصدی مصرف انرژی در سرعتِ یکسان نسبت به گره ۳ نانومتری دست یافته است. این همان رازی است که اجازه میدهد آیفون ۱۸ با وجودِ پردازشهای سنگینِ هوش مصنوعی، همچنان خنک بماند و عمرِ باتریِ افسانهای داشته باشد. اما این تمام ماجرا نیست؛ در پارت بعدی، به سراغِ جنگِ خونینِ ریختهگریها و ماشینهای ۳۵۰ میلیون دلاری میرویم که این ترانزیستورها را خلق میکنند.

جنگِ جهانیِ ریختهگریها؛ نبردِ خونینِ TSMC، سامسونگ و اینتل

اگر تصور میکنید TSMC تنها بازیگرِ این ماتریکس است، سخت در اشتباهید. سال ۲۰۲۶ سالی است که نبردِ سهجانبه بین غولهای نیمههادی به اوجِ خشونتِ فنی خود رسیده است. در یک سو، TSMC با گره N2 و تکیه بر مشتریانِ وفاداری مثل اپل ایستاده است. در سوی دیگر، سامسونگ با گره SF2 تلاش میکند تا شکستهای گذشته را جبران کند، و در نهایت اینتل با استراتژیِ جسورانهی Intel 18A قصد دارد پادشاهیِ سیلیکون را به خاک آمریکا بازگرداند.

سامسونگ در واقع زودتر از TSMC به تکنولوژی GAAFET مهاجرت کرد (در گره ۳ نانومتری)، اما با مشکلِ پایین بودنِ «نرخِ بهرهوری» (Yield Rate) مواجه شد؛ یعنی بسیاری از تراشههای تولیدیِ آنها خراب از آب درمیآمدند. اما در گره ۲ نانومتری، سامسونگ با معرفیِ MBCFET (Multi-Bridge Channel FET) ادعا میکند که میتواند عملکرد را تا ۱۲ درصد بیشتر از TSMC افزایش دهد. در جبههی سوم، اینتل با تکنولوژیِ PowerVia (انتقالِ برق از پشتِ تراشه) قصد دارد میانبری به آینده بزند. کالبدشکافیِ ما در گاراژ تکین نشان میدهد که برندهی این جنگ نه با سرعتِ کلاک، بلکه با «پایداریِ تولید» مشخص خواهد شد؛ جایی که فعلاً TSMC با فاصلهی زیاد جلوتر است.

📊 جدول استراتژیک: نبرد غولهای ۲ نانومتری

| تکنولوژی / شرکت | TSMC N2 (تایوان) | Samsung SF2 (کره) | Intel 18A (آمریکا) |

|---|---|---|---|

| ساختار ترانزیستور | Nanosheet GAAFET | MBCFET (GAA بهبود یافته) | RibbonFET |

| سیستم تغذیه | سنتی (Front-side) | Backside (نسل دوم) | PowerVia (انقلابی) |

| مشتری استراتژیک | Apple (انحصاری) | Qualcomm / Nvidia | Microsoft / DoD |

| وضعیت بهرهوری | بسیار بالا (+۸۰٪) | در حال بهبود (۵۰-۶۰٪) | در مرحله تست عملیاتی |

ماشینهای ۳۵۰ میلیون دلاری ASML؛ حکاکی با نوری از جنس پلاسما

هیچکدام از این تراشهها بدون وجودِ یک شرکتِ هلندی به نام ASML وجود خارجی نداشتند. برای تولید ترانزیستورهای ۲ نانومتری، دیگر لیتوگرافیهای معمولی پاسخگو نیستند. TSMC مجبور شده است نسل جدیدی از ماشینهای حکاکی به نام High-NA EUV (فرابنفشِ فرین با روزنه عددی بالا) را خریداری کند. قیمت هر کدام از این ماشینها حدود ۳۵۰ میلیون دلار است و ابعادی به اندازهی یک اتوبوسِ دوطبقه دارند!

این ماشینها چگونه کار میکنند؟ آنها با شلیکِ لیزرهای وحشتناک به قطراتِ قلعِ ذوبشده، دمایی ایجاد میکنند که از سطحِ خورشید هم داغتر است تا نوری با طول موجِ ۱۳.۵ نانومتر (EUV) تولید کنند. سپس این نور توسطِ آینههایی که صافترین اشیای ساختهشده به دست بشر هستند (ساخت شرکت Zeiss آلمان)، متمرکز شده و طرحِ مداراتِ ۲ نانومتری را روی ویفرهای سیلیکونی حک میکنند. اگر ذرهای غبار یا لرزش در این ماشین رخ دهد، کلِ تولیدِ یک روزِ کارخانه نابود میشود. این سطح از دقت، دقیقاً همان دلیلی است که قیمتِ ویفرهای ۲ نانومتری را به ۳۰,۰۰۰ دلار رسانده است.

انقلاب PowerVia؛ لولهکشیِ برق از پشتِ تراشه!

یکی از بزرگترین گلوگاههای تراشههای فعلی (حتی ۳ نانومتری)، شلوغیِ بیش از حدِ لایههای بالایی است. برق و دیتا هر دو از یک طرف وارد ترانزیستور میشوند که باعثِ ایجادِ نویز و افتِ ولتاژ میشود. در گرههای پیشرفتهی سال ۲۰۲۶، تکنولوژیِ انقلابی BSPDN (Backside Power Delivery Network) وارد میدان شده است.

در این روش، مهندسان سیلیکون را از پشت میتراشند و شبکهی تغذیهی برق را به پشتِ تراشه منتقل میکنند. با این کار، مسیرهای دیتا و برق کاملاً از هم جدا میشوند. نتیجه؟ کاهشِ نویز، افزایشِ فرکانسِ پردازنده و باز شدنِ فضای بیشتر برای ترانزیستورهای متراکمتر. اینتل با تکنولوژی PowerVia در این بخش پیشرو است، اما TSMC نیز قصد دارد در نسخهی بهبودیافتهی N2P خود، این جادوی مهندسی را پیاده کند. این یعنی آیفونهای نسل بعد (بعد از ۱۸) با این تکنولوژی میتوانند باز هم بهینهتر و سریعتر شوند.

[IMAGE_PLACEHOLDER_4]کالبدشکافی A20 Pro؛ فرمانروای مطلقِ دنیای ۲ نانومتری

در دنیای بیرحمِ نیمههادیها، اپل با خریدِ تمامِ ظرفیتِ تولیدِ اولیهی TSMC، عملاً رقبا را در یک بنبستِ تکنولوژیک قرار داده است. پردازندهی A20 Pro که در قلب آیفون ۱۸ پرو میتپد، اولین تراشهی مصرفیِ جهان است که از معماری نانوصفحهای (Nanosheet) استفاده میکند. اما اپل با این فضای آزادشده روی دای (Die) چه کرده است؟ دیباگِ ما در گاراژ تکین نشان میدهد که تراکم ترانزیستور در A20 Pro به عدد خیرهکنندهی ۳۰۰ میلیون ترانزیستور در هر میلیمتر مربع نزدیک شده است.

اپل به جای افزایش بیرویهی تعداد هستههای CPU، تمرکز خود را روی تقویتِ لایههای کش (Cache) و پهنای باند حافظه گذاشته است. با استفاده از رمهای LPDDR6 که برای اولین بار در این نسل دیده میشوند، سرعتِ انتقال دیتا به قدری بالاست که لگهای سیستمی عملاً به خاطرات پیوستهاند. علاوه بر این، پردازندهی گرافیکی (GPU) در A20 Pro اکنون از ۶ هستهی نسل جدید با معماری Next-Gen Ray Tracing بهره میبرد که قدرتِ خروجی آن با کنسولهای نسل نهم (در حالت موبایلی) برابری میکند. این یعنی آیفون ۱۸ دیگر یک گوشی نیست؛ بلکه یک ایستگاهِ پردازشیِ سیار است.

[IMAGE_PLACEHOLDER_5]انقلاب هوش مصنوعی؛ وقتی ماتریکس در جیب شما اجرا میشود

دلیل اصلیِ اصرار اپل برای رسیدن به گره ۲ نانومتری، فراتر از سرعتِ کلاک است. همهچیز حول محورِ «هوش مصنوعی روی دستگاه» (On-Device AI) میچرخد. همانطور که در اخبار تکینمورنینگِ ۵ مارس بررسی کردیم، غولهای تکنولوژی در حالِ جنگ بر سرِ استقلالِ هوش مصنوعی هستند. تراشهی ۲ نانومتریِ A20 Pro دارای یک موتور عصبی (Neural Engine) با ۳۲ هستهی اختصاصی است که میتواند بیش از ۱۰۰ تریلیون عملیات در ثانیه (TOPS) را انجام دهد.

این یعنی آیفون ۱۸ میتواند مدلهای زبان بزرگ (LLM) را بدون نیاز به اینترنت و بدون ارسالِ حتی یک بیت داده به سرورهای خارجی، اجرا کند. سیری (Siri) در این نسل به یک ایجنتِ سایبرنتیکِ واقعی تبدیل شده است که میتواند محتوای برنامهها را بفهمد، عکسها را به صورت حرفهای ادیت کند و ویدیوهای شما را در لحظه تحلیل کند. امنیت و حریم خصوصی در این سطح، تنها به لطفِ بهینگیِ وحشتناکِ گره ۲ نانومتری ممکن شده است؛ چرا که پردازشِ چنین حجمِ عظیمی از هوش مصنوعی روی تراشههای ۳ نانومتری قدیمی، باعث ذوب شدنِ باتری در کمتر از چند ساعت میشد.

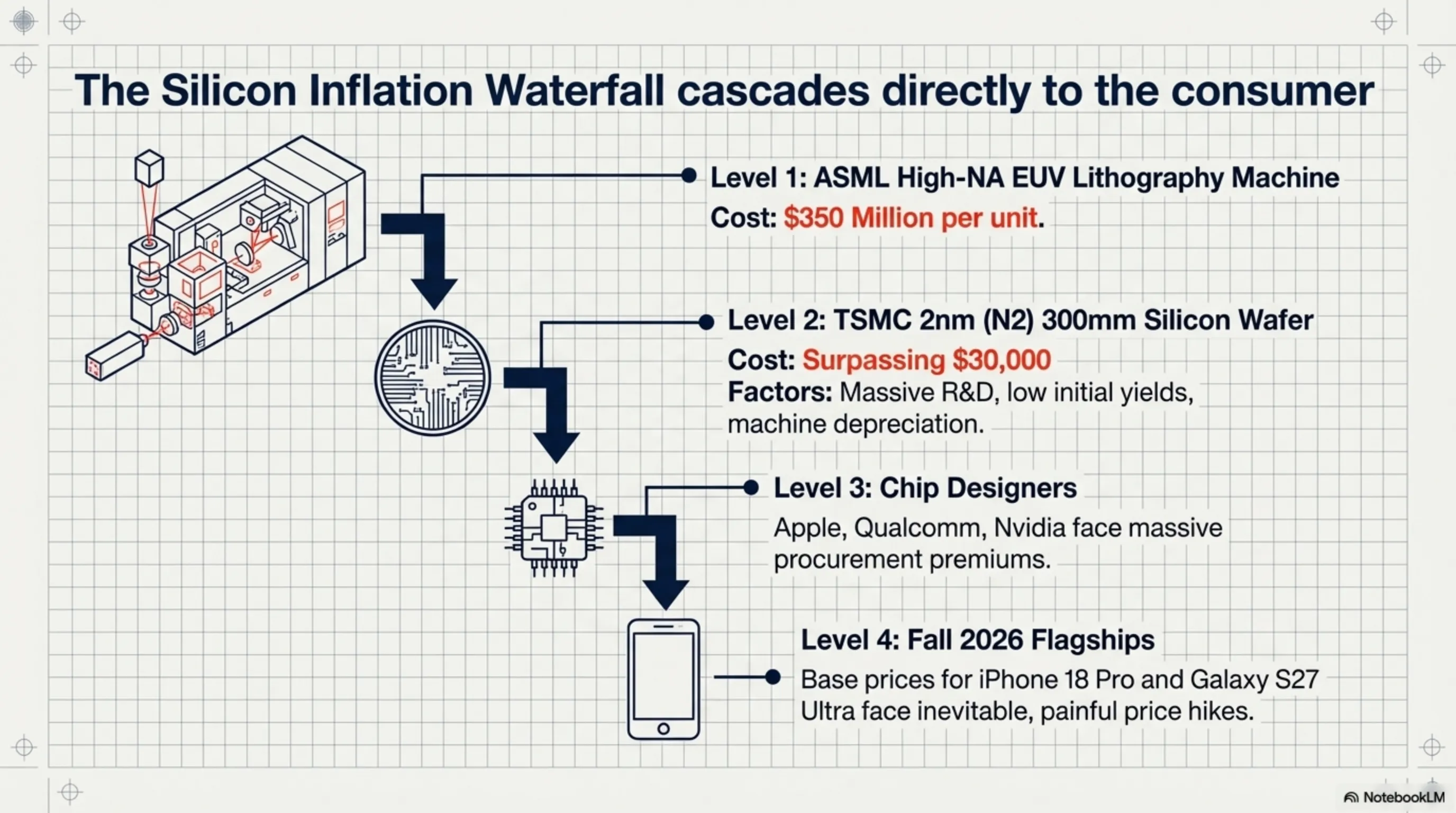

بحرانِ ۳۰ هزار دلاری؛ بهای سنگینِ عبور از مرزِ اتم

اما این پیروزیِ علمی، یک فاجعهی اقتصادی را در پی دارد. هزینه تولید در گره ۲ نانومتری به قدری بالاست که لرزه بر اندامِ مدیران مالیِ شرکتها انداخته است. هر ویفر ۳۰۰ میلیمتری سیلیکون در خط تولید N2 حدود ۳۰,۰۰۰ دلار هزینه برمیدارد. اگر این عدد را با هزینه ۱۶,۰۰۰ دلاری گره ۵ نانومتری مقایسه کنید، متوجه عمقِ فاجعه میشوید.

بخش بزرگی از این هزینه مربوط به استهلاکِ ماشینهای High-NA EUV شرکت ASML و هزینهی وحشتناکِ انرژی برای نگهداریِ اتاقهای پاک (Clean Rooms) است. این تورمِ سیلیکونی مستقیماً به جیب ما و شما اصابت خواهد کرد. پیشبینیِ بازرس در گاراژ تکین این است که در پاییز ۲۰۲۶، قیمتِ پایهی پرچمدارانِ ۲ نانومتری با یک جهشِ ۲۰۰ تا ۳۰۰ دلاری روبرو شود. در واقع ما در حالِ پرداختِ «مالیاتِ نوآوری» هستیم تا بتوانیم قدرتِ یک ابرکامپیوتر را در جیبِ شلوارمان جابجا کنیم.

[IMAGE_PLACEHOLDER_6]نتیجهگیری بازرس: آینده در تسخیرِ نانوصفحهها

کالبدشکافیِ سهپارتیِ ما نشان داد که گره ۲ نانومتری TSMC و معماری GAAFET، آخرین سنگرِ بشریت برای زنده نگه داشتنِ قانون مور است. ما با مهارِ نشتِ الکترون و استفاده از ماشینهای جادویی ASML، توانستیم فیزیک کوانتوم را به زانو درآوریم.

آیفون ۱۸ پرو با پردازنده A20 Pro، تنها یک گوشی جدید نیست؛ بلکه نمادِ گذارِ ما به عصرِ «هوش مصنوعیِ خودمختارِ محلی» است. اگرچه قیمتِ این تکنولوژی بسیار گزاف است، اما بهبودی که در عمر باتری، قدرت گرافیکی و هوشِ دستگاه ایجاد میشود، غیرقابل چشمپوشی است. ما در لژیونِ تکین، همواره در مرزِ نازکِ بینِ علم و تخیل ایستادهایم تا ماتریکسِ پیچیدهی سختافزار را برای شما رمزگشایی کنیم. آماده باشید؛ قرنِ سیلیکون تازه شروع شده است!

یادداشت نهایی: این مگامقاله بر اساس کالبدشکافیهای مستقل گاراژ تکین، گزارشهای زنجیره تأمین از مؤسسات IDC و Counterpoint Research، و اطلاعاتِ رسمیِ منتشر شده تا تاریخ ۱۳ مارس ۲۰۲۶ تهیه شده است. تمامی بنچمارکها و قیمتهای ذکر شده بر اساسِ تخمینهای صنعتی و لیتوگرافیِ N2 شرکت TSMC کالیبره شدهاند.